74107 IC – Dual J-K Flip-Flop with Clear (Reset)

🔲 74107 IC – Dual J-K Flip-Flop with Clear (Reset)

The 74107 is a Dual J-K Master-Slave Flip-Flop IC featuring asynchronous clear/reset (active LOW). Each flip-flop is edge-triggered and includes J, K, Clock (CLK), and Clear (CLR) inputs along with standard Q and Q̅ outputs. It is commonly used in digital sequential circuits such as frequency dividers, counters, and memory storage.

⚙️ Technical Specifications

| Parameter | Specification |

|---|---|

| Logic Family | TTL (74 series) |

| Flip-Flop Type | Master-Slave J-K |

| Number of Flip-Flops | 2 |

| Package Type | DIP-14 |

| Supply Voltage (Vcc) | 4.75V to 5.25V (Typically 5V) |

| Input Logic Levels | HIGH ≥ 2V, LOW ≤ 0.8V |

| Clock Trigger Type | Negative-edge triggered |

| Clear Input | Asynchronous, active LOW |

| Output Drive Current | ~8 mA |

| Operating Temperature | 0°C to +70°C |

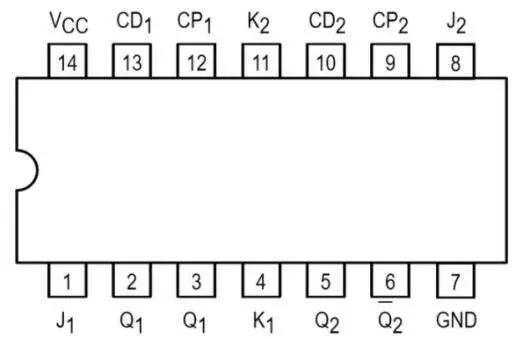

📌 Pin Configuration (DIP-14)

| Pin | Function | Pin | Function |

|---|---|---|---|

| 1 | 1CLR (Clear 1) | 14 | Vcc |

| 2 | 1CLK (Clock 1) | 13 | 2CLR (Clear 2) |

| 3 | 1K | 12 | 2CLK (Clock 2) |

| 4 | 1J | 11 | 2K |

| 5 | Q1 | 10 | 2J |

| 6 | Q̅1 | 9 | Q2 |

| 7 | GND | 8 | Q̅2 |

🧠 Logic Function – J-K Flip-Flop

| J | K | CLK ↓ | Q (Next) | Description |

|---|---|---|---|---|

| 0 | 0 | Falling | No Change | Memory |

| 0 | 1 | Falling | 0 | Reset |

| 1 | 0 | Falling | 1 | Set |

| 1 | 1 | Falling | Toggle | Invert Output |

| - | - | CLR = 0 | 0 | Asynchronous Reset |

🔄 The clear (CLR) input overrides the clock and forces Q = 0, Q̅ = 1 when active (LOW).

🛠️ Applications

Binary and ripple counters

Toggle circuits

Clock division

Frequency measurement

Sequential digital logic

Educational electronics